# **ARM Cortex-A8 CPU Module Family**

LITE Line

# **HARDWARE MANUAL**

<Page intentionally left blank>

# **Table of Contents**

| 1 Preface                                                     | 6  |

|---------------------------------------------------------------|----|

| 1.1 About this manual                                         | 6  |

| 1.2 Copyrights/Trademarks                                     | 6  |

| 1.3 Standards                                                 | 6  |

| 1.4 Disclaimers                                               | 6  |

| 1.5 Warranty                                                  | 7  |

| 1.6 Technical Support                                         |    |

| 1.7 Related documents                                         | 8  |

| 1.8 Conventions, Abbreviations, Acronyms                      | 8  |

| 2 Introduction                                                |    |

| 2.1 Product Highlights                                        | 12 |

| 2.2 Block Diagram                                             |    |

| 2.3 Feature Summary                                           |    |

| 3 Design overview                                             |    |

| 3.1 "Sitara" AM335x CPU                                       |    |

| 3.2 DDR3 memory bank                                          |    |

| 3.3 NOR flash bank                                            |    |

| 3.4 NAND flash bank                                           | 18 |

| 3.5 Memory Map                                                | 18 |

| 3.6 Power supply unit                                         |    |

| 3.7 CPU module connectors                                     |    |

| 4 Mechanical specifications                                   | 20 |

| 4.1 Board Layout                                              | 20 |

| 4.2 Connectors                                                |    |

| 5 Power, reset and control                                    | 23 |

| 5.1 Power Supply Unit (PSU) and recommended power-up sequence | 23 |

| 5.2 PMIC                                                      |    |

| 5.3 Reset scheme and voltage monitoring                       | 25 |

| 5.3.1 EXT PORSTn (J1.199)                                     |    |

| 5.3.2 PORSTn OUT (J1.170)                                     |    |

| 5.3.3 WARMRSTn (J1.197)                                       |    |

| 5.3.4 RTC PWRONRSTn (J1.195)                                  |    |

| 5.3.5 JTAG_TRSTn (J1.135)                                     |    |

| 5.3.6 PMIC_nRESPWRON (J1.191)                                 |    |

| 5.3.7 MRSTn (J1.193)                                          |    |

| 5.4 Boot options                                              |    |

| 5.4.1 Default boot configuration                              |    |

| 5.4.2 Boot sequence customization                             |    |

| 5.5 Clock scheme                                              |    |

| 5.6 Recovery                                                  |    |

| 5.6.1 JTAG Recovery                                           |    |

|                                                               |    |

| 5.6.2 UART Recovery                                                    |    |

|------------------------------------------------------------------------|----|

| 5.6.3 SD/MMC Recovery                                                  | 31 |

| 5.7 Multiplexing                                                       |    |

| 5.8 RTC                                                                | 32 |

| 5.9 Watchdog                                                           | 32 |

| 6 Pinout table                                                         | 33 |

| 6.1 Carrier board mating connector J1                                  | 35 |

| 7 Peripheral interfaces                                                | 51 |

| 7.1 Programmable Real-Time Unit and Industrial Communication Subsystem | 51 |

| 7.1.1 PRU signals                                                      | 53 |

| 7.2 Ethernet ports                                                     | 53 |

| 7.2.1 Ethernet 10/100                                                  | 54 |

| 7.2.2 Gigabit EMAC                                                     | 54 |

| 7.3 CAN ports                                                          | 55 |

| 7.3.1 DCAN0                                                            | 55 |

| 7.3.2 DCAN1                                                            | 56 |

| 7.4 UARTs                                                              | 56 |

| 7.4.1 UART0                                                            | 56 |

| 7.4.2 UART1                                                            | 57 |

| 7.4.3 UART2                                                            | 57 |

| 7.4.4 UART3                                                            | 58 |

| 7.4.5 UART3                                                            | 58 |

| 7.4.6 UART4                                                            | 58 |

| 7.4.7 UART5                                                            | 59 |

| 7.5 MMC/SD channels                                                    | 59 |

| 7.5.1 MMC/SD/SDIO0                                                     | 60 |

| 7.5.2 MMC/SD/SDIO 1                                                    | 60 |

| 7.5.3 MMC/SD/SDIO 2                                                    | 61 |

| 7.6 USB ports                                                          | 62 |

| 7.6.1 USB0                                                             | 62 |

| 7.6.2 USB1                                                             | 63 |

| 7.7 Touchscreen / ADC                                                  | 63 |

| 7.8 LCD controller                                                     | 64 |

| 7.9 SPI buses                                                          | 65 |

| 7.9.1 SPI channel 0                                                    | 65 |

| 7.9.2 SPI channel 1                                                    | 66 |

| 7.10 I2C buses                                                         | 66 |

| 7.10.1 I2C channel 0                                                   | 67 |

| 7.10.2 I2C channel 1                                                   |    |

| 7.10.3 I2C channel 2                                                   |    |

| 7.11 EEPROM                                                            |    |

| 7.12 Local Bus (GPMC)                                                  |    |

| 7 13 GPIOs                                                             | 72 |

| 7.14 Timers                                                     | 72 |

|-----------------------------------------------------------------|----|

| 7.15 Pulse width modulation subsystem (PWMSS)                   | 73 |

| 7.15.1 eHRPWM 0                                                 | 73 |

| 7.15.2 eHRPWM 1                                                 | 74 |

| 7.15.3 eHRPWM 2                                                 | 74 |

| 7.15.4 eCAP                                                     | 74 |

| 7.15.5 eQEP 0                                                   | 75 |

| 7.15.6 eQEP 1                                                   | 75 |

| 7.15.7 eQEP 2                                                   | 76 |

| 8 Operational characteristics                                   | 77 |

| 8.1 Maximum ratings                                             | 77 |

| 8.2 Recommended ratings                                         | 77 |

| 8.3 Power consumption                                           | 77 |

| 8.3.1 Set 1                                                     |    |

| 8.3.1.1Results                                                  |    |

| 8.4 Heat Dissipation                                            |    |

| 9 Application notes                                             | 79 |

| Index of Tables  Tab. 1: Related documents                      |    |

| Tab. 2: Abbreviations and acronyms used in this manual          |    |

| Tab. 3: CPU, Memories, Busses  Tab. 4: Peripherals              |    |

| Tab. 5: Electrical, Mechanical and Environmental Specifications |    |

| Tab. 6: AM335x part number comparison                           |    |

| Tab. 7: DDR3 specifications                                     |    |

| Tab. 8: NOR flash specifications                                |    |

| Tab. 9: NAND flash specifications                               |    |

| <b>r</b>                                                        |    |

| Illustration Index                                              |    |

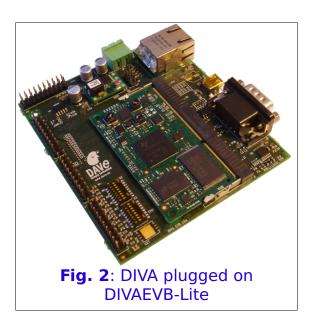

| Fig. 1: DIVA CPU module                                         | 11 |

| Fig. 2: DIVA plugged on DIVAEVB-Lite                            | 11 |

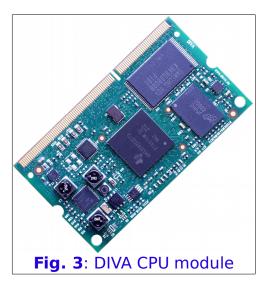

| Fig. 3: DIVA CPU module                                         |    |

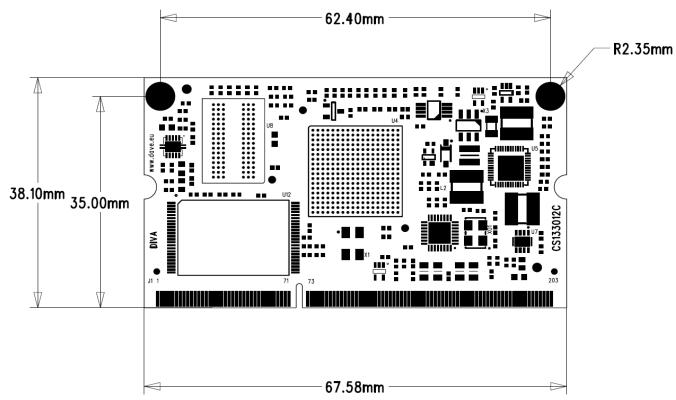

| Fig. 4: Board layout - top view                                 |    |

| Fig. 5: DIVA module - Side view                                 |    |

| Fig. 6: Connectors layout                                       |    |

| Fig. 7: DIVA power-up sequence                                  | 23 |

| Fig. 8: DIVA Paset scheme                                       | 25 |

# 1 Preface

#### 1.1 About this manual

This Hardware Manual describes the DIVA CPU module series, their design and functions.

Precise specifications for the Texas Instruments AM335x processors can be found in the CPU datasheets and/or reference manuals.

#### 1.2 Copyrights/Trademarks

Ethernet® is a registered trademark of XEROX Corporation.

All other products and trademarks mentioned in this manual are property of their respective owners.

All rights reserved. Specifications may change any time without notification.

#### 1.3 Standards

**DAVE Embedded Systems** is certified to ISO 9001 standards.

#### 1.4 Disclaimers

**DAVE Embedded Systems** does not assume any responsibility for availability, supply and support related to all products mentioned in this manual that are not strictly part of the DIVA CPU module.

DIVA CPU Modules are not designed for use in life support appliances, devices, or systems where malfunctioning of these products can reasonably be expected to result in personal injury. **DAVE Embedded Systems** customers who are using or selling these products for use in such applications do so at their own risk and agree to fully indemnify **DAVE Embedded Systems** for any damage resulting from such improper use or sale.

#### 1.5 Warranty

DIVA is guaranteed against defects in material and workmanship for the warranty period from the shipment date. During the warranty period, **DAVE Embedded Systems** will at its discretion decide to repair or replace defective products. Within the warranty period, the repair of products is free of charge provided that warranty conditions are observed.

The warranty does not apply to defects resulting from improper or inadequate maintenance or handling by the customer, unauthorized modification or misuse, operation outside of the product's specifications or improper installation or maintenance.

**DAVE Embedded Systems** will not be responsible for any defects or damages to other products not supplied by **DAVE Embedded Systems** that are caused by a faulty DIVA module.

#### 1.6 Technical Support

We are committed to making our products easy to use and will help customers use our CPU modules in their systems.

Technical support is delivered through email for registered kits owners. Support requests can be sent to <a href="mailto:support-diva@dave.eu">support-diva@dave.eu</a>. Software upgrades are available for download in the restricted download area of **DAVE Embedded Systems** web site: <a href="http://www.dave.eu/reserved-area">http://www.dave.eu/reserved-area</a>. An account is required to access this area.

Please refer to our Web site at <a href="http://www.dave.eu/dave-cpu-module-am335x-diva.html">http://www.dave.eu/dave-cpu-module-am335x-diva.html</a> for the latest product documents, utilities, drivers, Product Change Notices, Board Support Packages, Application Notes, mechanical drawings and additional tools and software.

#### 1.7 Related documents

| Document                                                                                      | Location                                                         |

|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| <b>DAVE Embedded Systems</b> Developers Wiki                                                  | http://wiki.dave.eu/index.php/Main_Page                          |

| AM335x<br>Technical<br>Reference Manual                                                       | http://www.ti.com/lit/ug/spruh73h/spr<br>uh73h.pdf               |

| AM335x Portal (on<br>TI Embedded<br>Processors Wiki )                                         | http://processors.wiki.ti.com/index.ph<br>p/Sitara_AM335x_Portal |

| Integration guide<br>(on <b>DAVE</b><br><b>Embedded</b><br><b>Systems</b><br>Developers Wiki) | http://wiki.dave.eu/index.php/Integration_guide_%28Diva%29       |

**Tab. 1**: Related documents

# 1.8 Conventions, Abbreviations, Acronyms

| Abbreviation | Definition                          |  |

|--------------|-------------------------------------|--|

| BTN          | Button                              |  |

| DIVELK       | DIVA Embedded Linux Kit             |  |

| EMAC         | Ethernet Media Access Controller    |  |

| GPI          | General purpose input               |  |

| GPIO         | General purpose input and output    |  |

| GPO          | General purpose output              |  |

| PCB          | Printed circuit board               |  |

| PMIC         | Power Management Integrated Circuit |  |

| PRU          | Programmable Real-Time Unit         |  |

| PSU          | Power supply unit                   |  |

| Abbreviation | Definition                                  |  |

|--------------|---------------------------------------------|--|

| RTC          | Real time clock                             |  |

| SOC          | System-on-chip                              |  |

| SO-DIMM      | Small Outline Dual In-line Memory<br>Module |  |

| SOM          | System-on-module                            |  |

| WDT          | Watchdog                                    |  |

|              |                                             |  |

|              |                                             |  |

|              |                                             |  |

|              |                                             |  |

**Tab. 2**: Abbreviations and acronyms used in this manual

# **Revision History**

| Version | Date           | Notes                                                                                                                                                                          |

|---------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.9.0   | October 2012   | First Draft                                                                                                                                                                    |

| 1.0.0   | June 2013      | First official release                                                                                                                                                         |

| 1.0.1   | September 2013 | Minor fixes                                                                                                                                                                    |

| 1.0.2   | October 2013   | Fixed RTC_PWRONRSTn direction VAUX33 added to pinout table Fixed PMIC_VBACKUP information Fixed section 8.1 and 8.2 tables Added I2C pull-up/pull-down information Minor fixes |

| 1.0.3   | April 2014     | Minor fixes                                                                                                                                                                    |

| 1.0.4   | August 2014    | Updated block diagram Fixed PGOOD (VAUX33) description Minor fixes                                                                                                             |

| 1.0.5   | October 2013   | Pinout table fixes<br>Minor fixes                                                                                                                                              |

| 1.0.6   | June 2015      | Minor Fixes<br>Updated mechanical drawings                                                                                                                                     |

# 2 Introduction

DIVA is a family of system-on-modules (SOM) that belongs to **DAVE Embedded Systems LITE Line** product class. DIVA is

Fig. 1: DIVA CPU module

based on Texas Instruments "Sitara" AM335x Cortex-A8 application processor and is built with SO-DIMM 204 pin form factor.

DIVA offers lots of graphics, processing, peripherals and industrial interface options, allowing customers to implement cost-effective design.

The Programmable Real-Time Unit and Industrial Communication Subsystem (PRU-ICSS) adds further flexibility and enables additional peripheral interfaces and real-time protocols such as EtherCAT, PROFINET, EtherNet/IP, PROFIBUS, Ethernet Powerlink.

Typical applications for DIVA are:

- Industrial sensors and I/O units

- Industrial drives with integrated communications and multi-axis motor control

- Programmable logic/automation controllers (PLC/PAC) with integrated industrial communications such as PROFIBUS, CAN and Ethernet

- Home and Building Automation

#### 2.1 Product Highlights

- ARM Cortex-A8 architecture @ 275/500/600/720 MHz

- LITE Line

- "No-frills" CPU module

- SO-DIMM connector

- Great cost-efficiency

- Extended power supply range [3.6 - 5.5]V, power regulation on board

- Coprocessing modules

- NEON

- PowerVR SGX

- Crypto accelerator

- Industrial specification compliance

- Extended temperature range (-40°C/+85°C)

- Industrial-oriented interfaces set

- Programmable Real-Time Unit and Industrial Communication Subsystem (PRU-ICSS)

- Supports protocols such as EtherCAT, PROFIBUS, PROFINET, EtherNet/IP™, and more

- Peripherals Inside the PRU-ICSS: UART port with flow control pins, MII Ethernet ports, MDIO port, ...

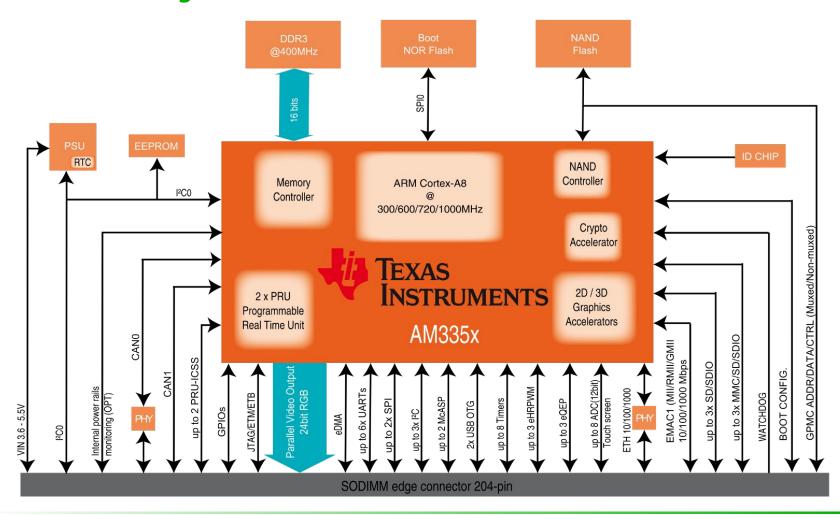

# 2.2 Block Diagram

June, 2015 13/79

# **2.3** Feature Summary

| Feature | Specifications                                                              | Options |

|---------|-----------------------------------------------------------------------------|---------|

| CPU     | "Sitara" AM335x<br>ARMv7 architecture<br>Cortex A8 @ 300/600/800/1000       |         |

| RAM     | 16-bit DDR3 @ 333 MHz<br>Up to 512 MB                                       |         |

| Storage | Flash NOR SPI<br>Flash NAND on Local bus<br>I <sup>2</sup> C 32 kbit EEPROM |         |

**Tab. 3**: CPU, Memories, Busses

| Feature                | Specifications                                                                                                   | Options |

|------------------------|------------------------------------------------------------------------------------------------------------------|---------|

| Graphics<br>Controller | Up to 24-Bits Data Output<br>Resolution Up to 2048x2048 (With<br>Maximum 126-MHz Pixel Clock)<br>TFT/RGB support |         |

| 2D/3D Engines          | NEON Multimedia SIMD coprocessor<br>PowerVR SGX 530 3D Accelerator                                               |         |

| Coprocessors           | Crypto Hardware Accelerator (AES, SHA, PKA, RNG) Up to 2x Programmable Realtime Units (PRUs)                     |         |

| USB                    | Up to 2x 2.0 OTG ports                                                                                           |         |

| UARTs                  | Up to 6x UART ports                                                                                              |         |

| GPIO                   | Up to 118 lines, shared with other functions (interrupts available)                                              |         |

| Input<br>interfaces    | Integrated 4/5/8-wire resistive touch screen controller                                                          |         |

| Networking             | Fast Ethernet with PHY<br>Additional MII/RMII/RGMII interface                                                    |         |

| CAN                    | Dual CAN controller (version 2 part A, B)                                                                        |         |

| SD/MMC                 | Up to 3x MMC/SD/SDIO Serial interfaces (up to 48 MHz)                                                            |         |

| Serial busses          | Up to 3x I <sup>2</sup> C channels<br>Up to 2x SPI channels                                                      |         |

| Audio                  | Up to 2x McASP interface                                                                                         |         |

| Timers/PWM             | Up to 4 programmable general purpose                                                                             |         |

| Feature       | Specifications                                                                                            | Options |

|---------------|-----------------------------------------------------------------------------------------------------------|---------|

|               | timers (PWM function available) PWMSS (Pulse width modulation subsystem) with 3x eHRPWM, 3x eCap, 3x eQEP |         |

| RTC           | On board, external battery powered                                                                        |         |

| Debug         | JTAG IEEE 1149.1 Test Access Port<br>ETM Port<br>ETB Port                                                 |         |

| Miscellaneous | Up to 8x 12-bit ADC channels                                                                              |         |

**Tab. 4**: Peripherals

| Feature                       | Specifications                             | Options |

|-------------------------------|--------------------------------------------|---------|

| Supply<br>Voltage             | [3.6 - 5.5] V, voltage regulation on board |         |

| Active power consumption      | Please refer to Power consumption section  |         |

| Dimensions                    | 67.5 mm x 38.3 mm                          |         |

| Weight                        | <tbd></tbd>                                |         |

| MTBF                          | <tbd></tbd>                                |         |

| Operation temperature         | 070 °C<br>-40+85 °C                        |         |

| Shock                         | <tbd></tbd>                                |         |

| Vibration                     | <tbd></tbd>                                |         |

| Connectors                    | 204-pin SO-DIMM                            |         |

| Connectors insertion/remo val | <tbd></tbd>                                |         |

**Tab. 5**: Electrical, Mechanical and Environmental Specifications

# 3 Design overview

The heart of DIVA module is composed by the following components:

- Texas Instruments AM335x processor

- Power supply unit

- DDR2 memory bank

- NOR and NAND flash banks

- 204 pin SO-DIMM connector with interfaces signals

This chapter shortly describes the main DIVA components.

#### 3.1 "Sitara" AM335x CPU

Sitara<sup>™</sup> ARM Cortex-A8 microprocessors (MPUs) are designed to optimize performance and peripheral support for customers in a variety of markets. AM335x Sitara<sup>™</sup> are highly-integrated, scalable and programmable CPU families from Texas Instruments and are enhanced with image, graphics processing, peripherals and industrial interface options such as EtherCAT and PROFIBUS. The following subsystems are part of the processor:

- Microprocessor unit (MPU) subsystem based on the ARM® Cortex™-A8 architecture:

- ARM Cortex-A8 RISC processor, with Neon<sup>™</sup> Floating-Point Unit, 32KB L1 Instruction Cache, 32KB L1 Data Cache and 256KB L2 Cache

- VFP coprocessor

- Debug subsystem (JTAG, CoreSight Embedded Trace Macrocell (ETM))

- General-Purpose Memory Controller (GPMC)

- PowerVR SGX 530 subsystem for vector/3D graphics acceleration to support display and gaming effects

- LCD and Touchscreen Controller

- Programmable Real-Time Unit and Industrial Communication Subsystem (PRU-ICSS)

- Integrated peripherals (USBs, EMACs, UARTs, ...)

The following table shows a **comparison** between the devices, highlighting the differences:

| Processor | PowerVR<br>SGX 3D | PRU-I<br>CSS | Ethercat | Crypto | Clock speed<br>(MHz)      |

|-----------|-------------------|--------------|----------|--------|---------------------------|

| AM3359    | YES               | YES          | YES      | YES    | 800                       |

| AM3358    | YES               | YES          | N.A.     | YES    | 600<br>800<br>1000        |

| AM3357    | N.A.              | YES          | YES      | YES    | 300<br>600<br>800         |

| AM3356    | N.A.              | YES          | N.A.     | YES    | 300<br>600<br>800         |

| AM3354    | YES               | N.A.         | N.A.     | YES    | 600<br>800<br>1000        |

| AM3352    | N.A.              | N.A.         | N.A.     | YES    | 300<br>600<br>800<br>1000 |

**Tab. 6**: AM335x part number comparison

### 3.2 DDR3 memory bank

DDR3 SDRAM memory bank is composed of a 16-bit width chip. The following table reports the SDRAM specifications:

| <b>CPU</b> connection | SDRAM bus |  |  |

|-----------------------|-----------|--|--|

| Size min              | 64 MB     |  |  |

| Size max              | 512 MB    |  |  |

| Width                 | 16 bit    |  |  |

| Speed                 | 333 MHz   |  |  |

Tab. 7: DDR3 specifications

#### 3.3 NOR flash bank

NOR flash is a Serial Peripheral Interface (SPI) device. This feature is optional and, when populated, the device is connected to AM335X\_SPI0 and can act as boot memory. The chip select is AM335X\_SPI0\_CS0.

The following table reports the NOR flash specifications:

| <b>CPU</b> connection | AM335X_SPI0 (CS0n) |  |  |  |  |

|-----------------------|--------------------|--|--|--|--|

| Size min              | 4 MByte            |  |  |  |  |

| Size max              | 128 MByte          |  |  |  |  |

| Bootable              | Yes                |  |  |  |  |

**Tab. 8**: NOR flash specifications

#### 3.4 NAND flash bank

On board main storage memory is a 8-bit wide NAND flash. This feature is optional and, when populated, the device is connected to the GPMC bus. The chip select is AM335X GPMC CS0n.

The following table reports the NAND flash specifications:

| <b>CPU</b> connection | GPMC bus (CS0n)              |  |  |  |  |

|-----------------------|------------------------------|--|--|--|--|

| Page size             | 512 byte, 2 kbyte or 4 kbyte |  |  |  |  |

| Size min              | 32 MByte                     |  |  |  |  |

| Size max              | 2 GByte                      |  |  |  |  |

| Width                 | 8 bit                        |  |  |  |  |

| Bootable              | Yes                          |  |  |  |  |

Tab. 9: NAND flash specifications

#### 3.5 Memory Map

This section will be completed in a future version of this manual.

#### 3.6 Power supply unit

DIVA, as the other LITE Line CPU modules, embeds all the

elements required for powering the unit, therefore power sequencing is self-contained and simplified. Nevertheless, power must be provided from carrier board, and therefore users should be aware of the ranges power supply can assume as well as all other parameters. For detailed information, please refer to Section 5.1.

#### 3.7 CPU module connectors

All interface signals provided by DIVA are routed through a 204 pin SO-DIMM connector. The host board must mount the mating connector and connect the desired peripheral interfaces according to DIVA pinout specifications.

For mechanical information, please refer to Section 4 (Mechanical specifications). For pinout and peripherals information, please refer to Sections 6 (Pinout table) and 7 (Peripheral interfaces).

# 4 Mechanical specifications

This chapter describes the mechanical characteristics of the DIVA module.

Mechanical drawings are available in DXF format from the DIVA page on DAVE Embedded Systems website http://http://www.dave.eu/dave-cpu-module-am335x-diva. html

### 4.1 Board Layout

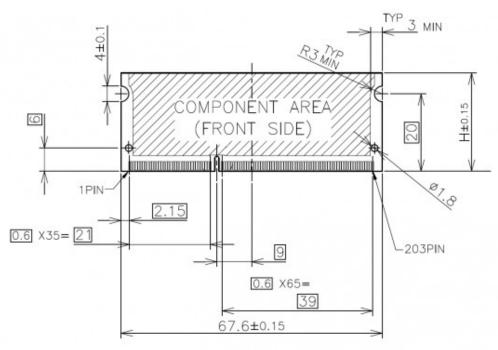

The following figure shows the physical dimensions of the DIVA module:

Fig. 4: Board layout - top view

• Board height: 38.3 mm

- Board width: 67.6 mm

- Height of all components is < 2.8 mm.

- PCB thickness is 1 mm.

The following figure highlights the maximum components' heights on DIVA module:

Fig. 5: DIVA module - Side view

#### 4.2 Connectors

The following figure shows the DIVA SODIMM connector layout:

Fig. 6: Connectors layout

The following table reports the connectors specifications:

| Part number Standard SO-DIMM 204-pin (DDR3) |                                                                                   |  |  |

|---------------------------------------------|-----------------------------------------------------------------------------------|--|--|

| Mating connectors                           | DDR3 SO-DIMM SOCKET Part number: TE Connectivity 2013289-1 (used on DIVAEVB-Lite) |  |  |

# 5 Power, reset and control

# 5.1 Power Supply Unit (PSU) and recommended power-up sequence

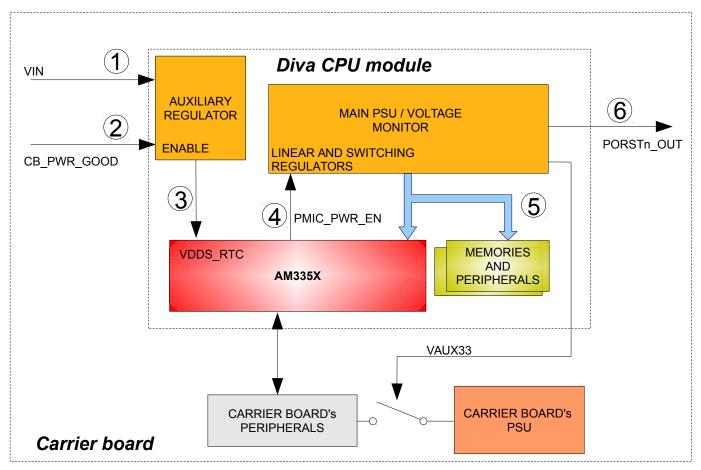

Implementing correct power-up sequence for AM335x processors family is not a trivial task because several power rails are involved. DIVA SOM simplifies this task and embeds all the needed circuitry. The following picture shows a

Fig. 7: DIVA power-up sequence

simplified block diagram of PSU/voltage monitoring circuitry:

The recommended power-up sequence is:

- 1. main power supply rail (VIN) ramps up

- 2. carrier board circuitry raises CB\_PWR\_GOOD; this indicates VIN rail is stable (1)

- 3. auxiliary regulator is enabled, thus processor's VDDS RTC domain is powered

- 4. processor raises PMIC\_PWR\_EN signal to start main PSU

- 5. this step is composed of two events:

- main PSU enables several voltage rails to complete CPU, memories and peripheral power up sequence

- VAUX33 signal is raised; this active-high signal indicates that SoM's I/O is powered. This signal can be used to manage carrier board power up sequence in order to prevent back powering (from SoM to carrier board or vice versa)

- 6. PORSTn\_OUT signal is raised to indicate that all power rails of SOM are stable

#### **5.2 PMIC**

Main PSU subsystem of DIVA SOM is based on Power Management Integrated Circuit (PMIC) Texas Instruments TPS65910A3A1. PMIC controls processor's power up sequence and sources the majority of power rails needed by AM335x.

Once processors is booted, it can control PMIC via the I2C0 bus to:

- set all the voltage needed by CPU in all operating conditions

- set RTC and control it

- manage power modes.

Besides I2C bus, PMIC has several control signals including:

PWRHOLD (input): This signal is connected to

<sup>1</sup> This step is not mandatory and VIN and CB\_PWR\_GOOD can be connected together. CB\_PWR\_GOOD is provided to prevent, if necessary, DIVA's PSU to turn on during ramp of carrier board VIN rail.

- processor's PMIC\_PWR\_EN and is used to initiate power up sequence.

- PMIC\_PWRON (input): A rising edge of this pin (automatically done at startup) the PMIC performs an OFF-to-ACTIVE state transition. On a falling edge of this pin, the PMIC performs an ACTIVE-to-OFF state transition. This signal is pulled-up to VIN through 10kOhm resistor.

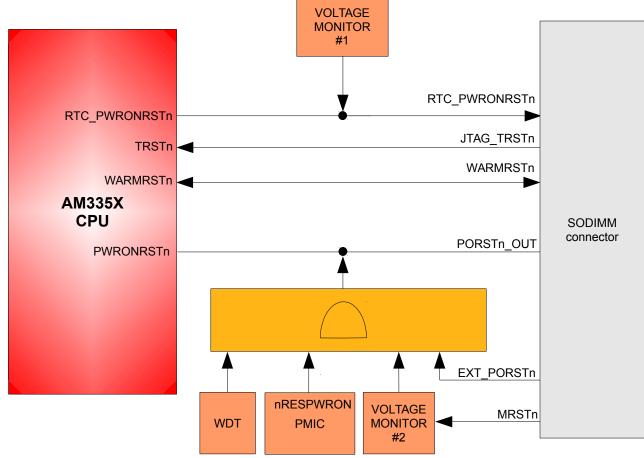

#### 5.3 Reset scheme and voltage monitoring

Fig. 8: DIVA Reset scheme

DIVA implements a flexible reset scheme that offers several different solutions for system integrators at carrier board level. The following picture shows a diagram of the reset scheme:

Apart from processor, there are four reset sources on DIVA SOM:

- 1. voltage monitor #1

- this device monitors VDDS\_RTC power rail and acts on processor's RTC PWRONRSTn signal

- 2. voltage monitor #2

- this device monitors processor's I/O power rail (3.3V) and acts on processor's PWRONRSTn signal

- 3. watchdog timer (please note that this watchdog timer has nothing to do with AM335x watchdog)

- this optional device (Maxim MAX6373KA+) acts on processor's PWRONRSTn signal

- 4. PMIC

- PMIC's nRESPWRON ouput acts on processor's PWRONRSTn signal.

In case a reset is issued by sources 2, 3 or 4 - eg. as consequence of a voltage glitch on power rail - or by an external source via EXT\_PORSTn signal, non-volatile memories are protected against spurious write operations that might occur.

Some of these reset signals are accessible by carrier board circuitry as described below.

#### 5.3.1 EXT PORSTn (J1.199)

The EXT\_PORSTn signal is an open-drain system reset input. When issued, a complete reset is done of all DIVA SOM circuitry. Note that the power sequence is not retriggered when a system reset is performed. Only CPU and peripherals on module are reset when this pin is in low state and they remain in reset state while the EXT\_PORSTn remains low. When the board is powered up, EXT\_PORSTn is automatically asserted by DIVA reset circuitry.

EXT\_PORSTn is pulled-up to processor's I/O voltage (3.3V) with 10kOhm resistor.

#### 5.3.2 PORSTn OUT (J1.170)

PORSTn\_OUT is an active-low push-pull ouput signal. PORSTn\_OUT is asserted whenever any of the following conditions are met:

- EXT PORSTn is asserted

- watchdog timer reset is asserted

- voltage monitor #2 reset is asserted

- PMIC nRESPWRON is asserted

PORSTn\_OUT is connected to processor's PWRONRSTn (also known as PORZ) signal.

PORSTn OUT is pulled-down with 10kOhm resistor.

#### 5.3.3 WARMRSTn (J1.197)

WARMRSTn is an active-low open-drain bidirectional signal. It is connected to processor's WARMRSTn (aka nRESETIN\_OUT) signal and it is asserted by processor itself as described by AM335x Technical Reference Manual.

WARMRSTn is pulled-up to processor's I/O voltage (3.3V) with 10kOhm resistor.

#### 5.3.4 RTC PWRONRSTn (J1.195)

RTC\_PORZ signal is connected to processor's RTC\_PWRONRSTn signal. It is an output-only signal, pulled-down with 100kOhm resistor. It only affects processor's RTC operations and registers.

#### 5.3.5 JTAG TRSTn (J1.135)

JTAG\_TRSTn is the test and emulation logic reset input. It is pulled-down with 10kOhm resistor.

#### 5.3.6 PMIC nRESPWRON (J1.191)

PMIC\_nRESPWRON is push-pull output signal. It is connected to PMIC's nRESPWRON. It is asserted by PMIC and acts on PORSTn\_OUT signal. PMIC\_nRESPWRON is pulled-down with

10kOhm resistor. For more details please refer to PMIC Data Manual.

#### 5.3.7 MRSTn (J1.193)

MRSTn is connected to the RESET IN input of the voltage monitor #2 (Maxim MAX6389XS31D3+T). This signal is compared to the voltage monitor internal +1.27V reference. If the voltage at RESET IN is less than 1.27V, reset asserts.

MRSTn is pulled-up to processor's I/O voltage (3.3V) with 10kOhm resistor.

#### 5.4 Boot options

AM335x processor provides several boot sequences selectable via BTMODE[15:0] bootstrap pins. In order to fully understand how boot works on DIVA platform, please refer to chapter 26 ("Initialization") of the AM335x Technical Reference Manual.

| Function          | Boot signals   | Default config | Selection        |

|-------------------|----------------|----------------|------------------|

| Crystal frequency | SYSBOOT[15:14] | 01             | 24 MHz           |

| Reserved          | SYSBOOT[13:12] | 00             | Normal operation |

| XIP/NAND boot     | SYSBOOT[11:10] | 00             | Non-muxed device |

| NAND ECC / WAIT   | SYSBOOT[9]     | 0              | ECC by ROM       |

| Bus width         | SYSBOOT[8]     | 0              | 8 bit device     |

| EMAC Phy mode     | SYSBOOT[7:6]   | 01             | RMII             |

| CLKOUT1           | SYSBOOT[5]     | 0              | CLKOUT1 disabled |

| Boot sequence     | SYSBOOT[4:0]   | 10111          | MMC0/SPI0/UART0  |

SYSBOOT[15:0] terminals are respectively LCD\_DATA[15:0] inputs, latched on the rising edge of PWRONRSTn. The booting device list is created based on the SYSBOOT pins. A booting device can be a memory booting device (soldered flash memory or temporarily booting device like memory card) or a peripheral interface connected to a host. The main loop of the booting procedure goes through the booting device list and tries to search for an image from the currently selected booting device. This loop is exited if a valid booting image is found and

successfully executed or upon watchdog expiration. The memory booting procedure is executed when the booting device type is one of NOR, NAND, MMC or SPI-EEPROM. The peripheral booting is executed when the booting device type is Ethernet, USB or UART.

#### 5.4.1 Default boot configuration

The default DIVA boot sequence is configured through a pull-up/pull-down resistors network. The following table describes the default boot signals (SYSBOOT[15:0]) configuration:

With these settings, the default boot sequence is:

- 1. MMC0

- 2. SPI0

- 3. UARTO

The internal bootrom tries each boot mode in sequence and stops when it finds a valid boot code.

#### Assuming that:

- default configuration is not changed,

- no boot MMC card is connected to processor's MMC0 interface,

- there's a valid boot code programmed in SPI memory

the actual boot sequence performed by ARM core will be:

- 1. bootrom: this is executed from internal ROM code memory

- 2. U-Boot 1. bootloader (1st stage) is

- copied from on-board NOR flash memory connected to SPI0 port to on-chip SRAM by bootrom

- executed from on-chip SRAM

- 3. U-Boot bootloader (2nd stage) is

- copied by U-Boot 1st stage from NOR flash memory connected to SPI0 port to SDRAM

- executed from SDRAM.

If no boot code is available in SPI NOR flash (for the bootrom this means that the first sector read returns 0xFFFFFFF) the bootrom tries UARTO peripheral booting.

#### 5.4.2 Boot sequence customization

DIVA default boot sequence can be changed by optional external circuitry implemented on the carrier board.

#### 5.5 Clock scheme

This section will be completed in a future version of this manual.

#### 5.6 Recovery

For different reason, starting from image corruption due power loss during upgrade or unrecoverable bug while developing a new U-Boot feature, the user will need, sooner or later, to recover (bare-metal restore) the DIVA SOM without using the bootloader itself. The following paragraphs introduce the available options. For further information, please refer to **DAVE Embedded Systems** Developers Wiki or contact the Technical Support Team.

#### 5.6.1 ITAG Recovery

JTAG recovery, though very useful (especially in development or production environment), requires dedicated hardware and software tools. DIVA provides the JTAG interface, which, besides the debug purpose, can be used for programming and recovery operations. For further information on how to use the ITAG interface, please contact the Technical Support Team.

#### 5.6.2 UART Recovery

UART recovery does not requires any specialized hardware, apart a PC and a DB9 serial cross cable. The boot sequence must include the UART option and a way to enable it. Then a simple procedure allow to load the 1st and 2nd stage bootloader from the serial line. When the 2nd stage bootloader

is running, reprogramming the flash memory is straightforward.

The UART boot uses **UART0** interface.

#### 5.6.3 SD/MMC Recovery

MMC recovery is a valuable option that requires no special hardware at all, apart a properly formatted MMC. The boot sequence must include the SD/MMC option and a way to enable it. When SD/MMC boot option is selected, bootrom looks for a valid boot sector on SD/MMC0. Once the board is running after booting from SD, reprogramming the flash memory is straightforward.

### 5.7 Multiplexing

AM335x pins can have up to eight alternate function modes. The I/O pins can be internally routed to/from one of several peripheral modules within the device: this routing is referred to as Pin Multiplexing. Pin Multiplexing allows software to choose the subset of internal signals which will be mapped to balls of the device for a given application. Pin multiplexing selects which one of several peripheral pin functions controls the pin's I/O buffer output data values.

Please note that pin mux configuration is a very critical step. Wrong configuration may lead to system instability, side effects or even damage the hardware permanently

Pin multiplexing configuration is quite complex in DIVA but a tool from TI, the Pin Mux Utility, can help to perform this operation. Software installation and generic usage documentation is available on this page of the TI Embedded Processors Wiki:

http://processors.wiki.ti.com/index.php/Pin\_Mux\_Utility\_for\_AR M MPU Processors

#### 5.8 RTC

The TPS65910A3 PMIC provides a real-time clock (RTC) resource with:

- Oscillator for 32.768-kHz crystal

- Date, time and calendar

- Alarm capability

- Backup power from external battery

Backup power is provided through the PMIC\_VBACKUP (J1.203) signal. If not used, PMIC\_VBACKUP must be externally connected to PMIC.VCC5 (VIN).

For a detailed description of RTC characteristics, please refer to the TPS65910A3 PMIC datasheet.

#### 5.9 Watchdog

An external watchdog (MAX6373 device) is connected to the AM335X\_GMII1\_TXD2 (J1.159) signal. During normal operation, the microprocessor should repeatedly toggle the watchdog input WDI (AM335X\_GMII1\_TXD2) before the selected watchdog timeout period elapses to demonstrate that the system is processing code properly. If the  $\mu P$  does not provide a valid watchdog input transition before the timeout period expires, the supervisor asserts a watchdog (WDO) output to signal that the system is not executing the desired instructions within the expected time frame. The watchdog output pulse is used to reset the  $\mu P$ .

The MAX6373 watchdog timer is pin-selectable and the timer can be configured through the WD\_SET0 (J1.7), WD\_SET1 (J1.9) and WD\_SET2 (J1.11) signals. As a default, the watchdog is configured through a pull-up/pull-down resistors network (WD\_SET[2..0] = 110) that keeps the watchdog timer inactive at startup. Startup delay ends when WDI sees its first level transition. The default watchdog timeout period is 10 s.

The configuration can be changed by optional external circuitry implemented on the carrier board.

# 6 Pinout table

This chapter contains the pinout description of the SO-DIMM-204 edge connector of the DIVA module. The following table reports the pin mapping of the module signals routed to the J1 204 connector's pins.

Each row in the pinout tables contains the following information:

| Pin                     | Reference to the connector pin                                                                                                                                                                                                                                                            |  |  |  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                | Pin (signal) name on the DIVA connector                                                                                                                                                                                                                                                   |  |  |  |

| Internal<br>Connections | Connections to the DIVA components:  CPU. <x>: pin connected to CPU pad named <x> PMIC.<x>: pin connected to the Power Manager IC ETHPHY.<x>: pin connected to the LAN PHY WDT.<x>: pin connected to the MAX6373 watchdog EEPROM.<x>: pin connected to the EEPROM</x></x></x></x></x></x> |  |  |  |

| Ball/pin #              | Component ball/pin number connected to signal                                                                                                                                                                                                                                             |  |  |  |

| <b>Supply Group</b>     | Power Supply Group                                                                                                                                                                                                                                                                        |  |  |  |

| Туре                    | Pin type: I = Input, O = Output, Z = High impedance, S = Supply voltage, G = Ground, A = Analog signal                                                                                                                                                                                    |  |  |  |

| Voltage                 | I/O voltage                                                                                                                                                                                                                                                                               |  |  |  |

The **Internal connection** column reports the name of the microprocessor signal, which in turn contains references to all the peripheral functions that can be associated to that pin. For example, the following pin name

#### CPU.

[I2C0\_SCL/TIMER7/UART2\_RTSN/ECAP1\_IN\_PWM1\_OUT////GPIO3\_6]

means that the pin can be used as:

- I2C0\_SCL: I2C channel 0, clock signal

- TIMER7: timer signal 7

- UART2\_RTSN: UART port 2, Request to Send signal

- ECAP1\_IN\_PWM1\_OUT: Enhanced Capture 1 input or Auxiliary PWM1 output

#### • GP3\_6: General Purpose I/O port 3, channel 6

The following table reports all the function names that can be found on the **Internal connection** and the associated description.

| Function name | Description                                                                      |

|---------------|----------------------------------------------------------------------------------|

| EMACx         | Ethernet MAC. "x" represents the port number (0 or 1)                            |

| UARTx         | UART port. "x" represents the port number (0 to 5)                               |

| GPIOx_y       | General Purpose I/O port. "x" represents the port number (0 to 3)                |

| SPIx          | SPI channel. "x" represents the channel number (0 to 3)                          |

| DCANx         | Controller Area Network module. "x" represents the module number (0 to 1)        |

| ММСх          | MMC/SD/SDIO interfaces. "x" represents the interface number (0 to 2)             |

| MCAx          | Multi-Channel Audio Serial Port (McASP). "x" represents the port number (0 to 5) |

| I2Cx          | I2C channel. "x" represents the channel number (0 to 3)                          |

# **6.1** Carrier board mating connector J1

| Pin | Pin Name         | Internal Connections                                                                                                         | Ball/<br>pin # | Supply<br>Group | Туре | Voltage | Note                                                |

|-----|------------------|------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|------|---------|-----------------------------------------------------|

| 1   | DGND             | DGND                                                                                                                         | -              |                 |      |         |                                                     |

| 2   | AM335X_GPMC_WPn  | CPU. [GPMC_WPN/GMII2_RXERR/GPMC_CSN5/RMI I2_RXERR/MMC2_SDCD/PR1_MII1_TXEN/UAR T4_TXD/GPIO0_31]                               | U17            |                 |      |         |                                                     |

| 3   | AM335X_I2C0_SCL  | CPU. [I2C0_SCL/TIMER7/UART2_RTSN/ECAP1_IN_P WM1_OUT////GPIO3_6]                                                              | C16            |                 |      |         | Internally connected to a 10K pull-up resistor      |

| 4   | AM335X_GPMC_CS0n | CPU.[GPMC_CSN0//////GPIO1_29]                                                                                                | V6             |                 |      |         | Internally connected to the NAND flash (if present) |

| 5   | AM335X_I2C0_SDA  | CPU. [I2C0_SDA/TIMER4/UART2_CTSN/ECAP2_IN_ PWM2_OUT////GPIO3_5]                                                              | C17            |                 |      |         | Internally connected to a 10K pull-up resistor      |

| 6   | AM335X_GPMC_CS1n | CPU. [GPMC_CSN1/GPMC_CLK/MMC1_CLK/PR1_E DIO_DATA_IN6/PR1_EDIO_DATA_OUT6/PR1_P RU1_PRU_R30_12/PR1_PRU1_PRU_R31_12/G PIO1_30]  | U9             |                 |      |         |                                                     |

| 7   | WD_SET0          | WDT.SET0                                                                                                                     | 4              |                 |      |         |                                                     |

| 8   | AM335X_GPMC_CS2n | CPU. [GPMC_CSN2/GPMC_BE1N/MMC1_CMD/PR1_ EDIO_DATA_IN7/PR1_EDIO_DATA_OUT7/PR1_ PRU1_PRU_R30_13/PR1_PRU1_PRU_R31_13/ GPIO1_31] | V9             |                 |      |         |                                                     |

| 9   | WD_SET1          | WDT.SET1                                                                                                                     | 5              |                 |      |         |                                                     |

| 10  | AM335X_GPMC_CS3n | CPU. [GPMC_CSN3///MMC2_CMD/PR1_MII0_CRS/PR1_MDIO_DATA/EMU4/GPIO2_0]                                                          | T13            |                 |      |         |                                                     |

| 11  | WD_SET2          | WDT.SET2                                                                                                                     | 6              |                 |      |         |                                                     |

| 12  | DGND             | DGND                                                                                                                         | -              |                 |      |         |                                                     |

| 13  | EEPROM_WP        | EEPROM.WP                                                                                                                    | 7              |                 |      |         |                                                     |

| 14 | AM335X_GPMC_CLK      | CPU.<br>[GPMC_CLK/LCD_MEMORY_CLK/GPMC_WAIT<br>1/MMC2_CLK/PR1_MII1_CRS/PR1_MDIO_MDC<br>LK/MCASP0_FSR/GPIO2_1]             | V12 |                                                        |

|----|----------------------|--------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------|

| 15 | EEPROM A1            | EEPROM.A1                                                                                                                | 2   |                                                        |

| 16 | AM335X_GPMC_WEn      | CPU.[GPMC_WEN//TIMER6/////GPIO2_4]                                                                                       | U6  | Internally connected to the NAND flash (if present)    |

| 17 | EEPROM A0            | EEPROM.A0                                                                                                                | 1   |                                                        |

| 18 | AM335X_GPMC_OEn_REn  | CPU.[GPMC_OEN_REN//TIMER6////GPIO2_4]                                                                                    | Т7  | Internally connected to the NAND flash (if present)    |

| 19 | AM335X EXT WAKEUP    | CPU.EXT WAKEUP                                                                                                           | C5  |                                                        |

| 20 | AM335X_GPMC_ADVn_ALE | CPU.[GPMC_ADVN_ALE//TIMER4/////GPIO2_2]                                                                                  | R7  | Internally connected to the NAND flash (if present)    |

| 21 | DGND                 | DGND                                                                                                                     | -   |                                                        |

| 22 | AM335X_GPMC_BE0n_CLE | CPU.[GPMC_BE0N_CLE//TIMER5/////GPIO2_5]                                                                                  | Т6  | Internally connected to the NAND flash (if present)    |

| 23 | AM335X_RMII1_REFCLK  |                                                                                                                          | H18 | HW option (not connected by default)                   |

| 24 | AM335X_GPMC_BE1n     | CPU. [GPMC_BE1N/GMII2_COL/GPMC_CSN6/MMC2 DAT3/GPMC_DIR/PR1_MII1_RXLINK/MCASP0 ACLKR/GPI01_28]                            | U18 |                                                        |

| 25 | AM335X_UART0_TXD     | CPU.<br>[UART0_TXD/SPI1_CS1/DCAN0_RX/I2C2_SCL<br>/ECAP1_IN_PWM1_OUT/PR1_PRU1_PRU_R30<br>15/PR1_PRU1_PRU_R31_15/GPIO1_11] | E16 |                                                        |

| 26 | AM335X_GPMC_WAIT     | CPU. [GPMC_WAIT0/GMII2_CRS/GPMC_CSN4/RMII 2_CRS_DV/MMC1_SDCD/PR1_MII1_COL/UAR T4_RXD/GPI00_30]                           | T17 | Internally connected to the NAND flash<br>(if present) |

| 27 | AM335X_UART0_RXD     | CPU. [UARTO_RXD/SPI1_CS0/DCANO_TX/I2C2_SDA /ECAP2_IN_PWM2_OUT/PR1_PRU1_PRU_R30 14/PR1_PRU1_PRU_R31_14/GPIO1_10]          | E15 |                                                        |

| 28 | AM335X_GPMC_A0       | CPU. [GPMC_A0/GMII2_TXEN/RGMII2_TCTL/RMII2_ TXEN/GPMC_A16/PR1_MII_MT1_CLK/EHRPW M1_TRIPZONE_INPUT/GPIO1_16]              | R13 |                                                        |

| 29 | AM335X_UART0_RTSn    |                                                                                                                          | E17 |                                                        |

|    |                      | [UARTO_RTSN/UART4_TXD/DCAN1_RX/I2C1_                                                                                     |     |                                                        |

|    |                   | SCL/SPI1_D1/SPI1_CS0/PR1_EDC_SYNC1_OU                                                            |     |  |  |  |

|----|-------------------|--------------------------------------------------------------------------------------------------|-----|--|--|--|

|    |                   | T/GPIO1_9]                                                                                       |     |  |  |  |

| 30 | AM335X_GPMC_A1    | CPU. [GPMC_A1/GMII2_RXDV/RGMII2_RCTL/MMC2 _DAT0/GPMC_A17/PR1_MII1_TXD3/EHRPWM 0_SYNCO/GPIO1_17]  |     |  |  |  |

| 31 | AM335X_UART0_CTSn | [UARTO_CTSN/UART4_RXD/DCAN1_TX/I2C1_<br>SDA/SPI1_D0/TIMER7/PR1_EDC_SYNC0_OUT<br>/GPIO1_8]        | E18 |  |  |  |

| 32 | DGND              | DGND                                                                                             | -   |  |  |  |

| 33 | AM335X_UART1_TXD  | CPU. [UART1_TXD/MMC2_SDWP/DCAN1_RX/I2C1_ SCL//PR1_UART0_TXD/PR1_PRU0_PRU_R31_ 16/GPIO0_15]       | D15 |  |  |  |

| 34 | AM335X_GPMC_A2    | CPU. [GPMC_A2/GMII2_TXD3/RGMII2_TD3/MMC2_ DAT1/GPMC_A18/PR1_MII1_TXD2/EHRPWM1 A/GPIO1_18]        | U14 |  |  |  |

| 35 | AM335X_UART1_RXD  | CPU. [UART1_RXD/MMC1_SDWP/DCAN1_TX/I2C1_ SDA//PR1_UART0_RXD/PR1_PRU1_PRU_R31_ 16/GPI00_14]       | D16 |  |  |  |

| 36 | AM335X_GPMC_A3    | CPU. [GPMC_A3/GMII2_TXD2/RGMII2_TD2/MMC2_ DAT2/GPMC_A19/PR1_MII1_TXD1/EHRPWM1 B/GPIO1_19]        | T14 |  |  |  |

| 37 | AM335X_UART1_RTSn | CPU. [UART1_RTSN/TIMER5/DCAN0_RX/I2C2_SCL/ SPI1_CS1/PR1_UART0_RTS_N/PR1_EDC_LATC H1_IN/GPI00_13] |     |  |  |  |

| 38 | AM335X_GPMC_A4    | CPU. [GPMC_A4/GMII2_TXD1/RGMII2_TD1/RMII2_ TXD1/GPMC_A20/PR1_MII1_TXD0/EQEP1A_I N/GPIO1_20]      | R14 |  |  |  |

| 39 | AM335X_UART1_CTSn | CPU. [UART1_CTSN/TIMER6/DCAN0_TX/I2C2_SDA/ SPI1_CS0/PR1_UART0_CTS_N/PR1_EDC_LAT CH0_IN/GPIO0_12] | D18 |  |  |  |

| 40 | AM335X_GPMC_A5   | [GPMC_A5/GMII2_TXD0/RGMII2_TD0/RMII2_<br>TXD0/GPMC_A21/PR1_MII1_RXD3/EQEP1B_I                                         | V15 |                                                           |

|----|------------------|-----------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------|

| 41 | DGND             | N/GPIO1_21] DGND                                                                                                      |     |                                                           |

| 42 | AM335X_GPMC_A6   | CPU. [GPMC_A6/GMII2_TXCLK/RGMII2_TCLK/MMC 2_DAT4/GPMC_A22/PR1_MII1_RXD2/EQEP1_I NDEX/GPIO1 22]                        | U15 |                                                           |

| 43 | AM335X_SPI0_SCLK | CPU. [SPI0_SCLK/UART2_RXD/I2C2_SDA/EHRPWM 0A/PR1_UART0_CTS_N/PR1_EDI0_SOF/EMU2 /GPI00_2]                              | A17 | Internally connected to the NOR SPI<br>flash (if present) |

| 44 | AM335X_GPMC_A7   | CPU. [GPMC_A7/GMII2_RXCLK/RGMII2_RCLK/MMC 2_DAT5/GPMC_A23/PR1_MII1_RXD1/EQEP1_ STROBE/GPIO1_23]                       | T15 |                                                           |

| 45 | AM335X_SPI0_D0   | CPU. [SPIO_DO/UART2_TXD/I2C2_SCL/EHRPWM0B /PR1_UART0_RTS_N/PR1_EDIO_LATCH_IN/EM U3/GPIO0_3]                           | B17 | Internally connected to the NOR SPI<br>flash (if present) |

| 46 | AM335X_GPMC_A8   | CPU. [GPMC_A8/GMII2_RXD3/RGMII2_RD3/MMC2_ DAT6/GPMC_A24/PR1_MII1_RXD0/MCASP0_A CLKX/GPI01_24]                         | V16 |                                                           |

| 47 | AM335X_SPI0_D1   | CPU. [SPI0_D1/MMC1_SDWP/I2C1_SDA/EHRPWM0 TRIPZONE_INPUT/PR1_UART0_RXD/PR1_ED IO_DATA_IN0/PR1_EDIO_DATA_OUT0/GPIO0_ 4] | B16 | Internally connected to the NOR SPI<br>flash (if present) |

| 48 | AM335X_GPMC_A9   | CPU. [GPMC_A9/GMII2_RXD2/RGMII2_RD2/MMC2_DAT7/GPMC_A25/PR1_MII_MR1_CLK/MCASP0_FSX/GPI01_25]                           | U16 |                                                           |

| 49 | AM335X_SPI0_CS0  | CPU. [SPIO_CSO/MMC2_SDWP/I2C1_SCL/EHRPWM 0_SYNCI/PR1_UART0_TXD/PR1_EDIO_DATA_I N1/PR1_EDIO_DATA_OUT1/GPIO0_5]         | A16 | Internally connected to the NOR SPI<br>flash (if present) |

| 50 | AM335X_GPMC_A10  | CPU.                                                                                                                  | T16 |                                                           |

|    |                             | [GPMC_A10/GMII2_RXD1/RGMII2_RD1/RMII2<br>RXD1/GPMC_A26/PR1_MII1_RXDV/MCASP0_<br>AXR0/GPIO1_26] |     |                                |                          |

|----|-----------------------------|------------------------------------------------------------------------------------------------|-----|--------------------------------|--------------------------|

| 51 | AM335X_SPI0_CS1             | CPU. [SPI0_CS1/UART3_RXD/ECAP1_IN_PWM1_OU T/MMC0_POW/XDMA_EVENT_INTR2/MMC0_S DCD/EMU4/GPI00_6] |     |                                |                          |

| 52 | DGND                        | DGND                                                                                           | -   |                                |                          |

| 53 | USB0_CE                     | CPU.USB0_CE                                                                                    | M15 |                                |                          |

| 54 | AM335X_GPMC_A11             | CPU. [GPMC_A11/GMII2_RXD0/RGMII2_RD0/RMII2 _RXD0/GPMC_A27/PR1_MII1_RXER/MCASP0_ AXR1/GPI01_27] | V17 |                                |                          |

| 55 | USB0_ID                     | CPU.USB0_ID                                                                                    | P16 |                                |                          |

| 56 | AM335X_GPMC_AD0             | CPU.[GPMC_AD0/MMC1_DAT0/////GPIO1_0]                                                           | U7  | Internally con<br>(if present) | nected to the NAND flash |

| 57 | USB0_DP                     | CPU.USB0_DP                                                                                    | N17 |                                |                          |

| 58 | AM335X_GPMC_AD1             | CPU.[GPMC_AD1/MMC1_DAT1/////GPIO1_1]                                                           | V7  | Internally con<br>(if present) | nected to the NAND flash |

| 59 | USB0_DM                     | CPU.USB0_DM                                                                                    | N18 |                                |                          |

| 60 | AM335X_GPMC_AD2             | CPU.[GPMC_AD2/MMC1_DAT2/////GPIO1_2]                                                           | R8  | Internally con<br>(if present) | nected to the NAND flash |

| 61 | DGND                        | DGND                                                                                           | -   |                                |                          |

| 62 | AM335X_GPMC_AD3             | CPU.[GPMC_AD3/MMC1_DAT3/////GPIO1_3]                                                           | Т8  | Internally con<br>(if present) | nected to the NAND flash |

| 63 | USB0_DRVVBUS                | CPU.USB0_DRVVBUS                                                                               | F16 |                                |                          |

| 64 | AM335X_GPMC_AD4             | CPU.[GPMC_AD4/MMC1_DAT4/////GPIO1_4]                                                           | U8  | Internally con<br>(if present) | nected to the NAND flash |

| 65 | VUSB_VBUS0                  | CPU.USB0_VBUS                                                                                  | P15 |                                |                          |

| 66 | AM335X_GPMC_AD5             | CPU.[GPMC_AD5/MMC1_DAT5/////GPIO1_5]                                                           | V8  | Internally con<br>(if present) | nected to the NAND flash |

| 67 | AM335x_EXTINTn              | CPU.NMIn                                                                                       | B18 |                                |                          |

| 68 | AM335X_GPMC_AD6             | CPU.[GPMC_AD6/MMC1_DAT6/////GPIO1_6]                                                           | R9  | Internally con<br>(if present) | nected to the NAND flash |

| 69 | AM335X_XDMA_EVENT_IN<br>TR0 | CPU. [XDMA_EVENT_INTRO//TIMER4/CLKOUT1/SPI 1_CS1/PR1_PRU1_PRU_R31_16/EMU2/GPIO0 _19]           |     |                                |                          |

| 70 | AM335X_GPMC_AD7             | CPU.[GPMC_AD7/MMC1_DAT7/////GPIO1_7]                                                                    | Т9  | Internally connected to the NAND flash (if present) |

|----|-----------------------------|---------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------|

| 71 | AM335X_XDMA_EVENT_IN<br>TR1 | CPU. [XDMA_EVENT_INTR1//TCLKIN/CLKOUT2/TIM ER7/PR1_PRU0_PRU_R31_16/EMU3/GPIO0_2 0]                      | D14 |                                                     |

| 72 | DGND                        | DGND                                                                                                    | -   |                                                     |

| 73 | USB1_CE                     | CPU.USB1_CE                                                                                             | P18 |                                                     |

| 74 | AM335X_GPMC_AD8             | CPU. [GPMC_AD8/LCD_DATA23/MMC1_DAT0/MMC 2_DAT4/EHRPWM2A/PR1_MII_MT0_CLK//GPI 00_22]                     | U10 |                                                     |

| 75 | USB1_ID                     | CPU.USB1_ID                                                                                             | P17 |                                                     |

| 76 | AM335X_GPMC_AD9             | CPU. [GPMC_AD9/LCD_DATA22/MMC1_DAT1/MMC 2_DAT5/EHRPWM2B/PR1_MII0_COL//GPIO0_ 23]                        | T10 |                                                     |

| 77 | USB1 DP                     | CPU.USB1 DP                                                                                             | R17 |                                                     |

| 78 | AM335X_GPMC_AD10            | CPU. [GPMC_AD10/LCD_DATA21/MMC1_DAT2/MM C2_DAT6/EHRPWM2_TRIPZONE_INPUT/PR1_ MII0_TXEN//GPIO0_26]        | T11 |                                                     |

| 79 | USB1 DM                     | CPU.USB1 DM                                                                                             | R18 |                                                     |

| 80 | AM335X_GPMC_AD11            | CPU. [GPMC_AD11/LCD_DATA20/MMC1_DAT3/MM C2_DAT7/EHRPWM2_SYNCO/PR1_MII0_TXD3 //GPIO0_27]                 | U12 |                                                     |

| 81 | DGND                        | DGND                                                                                                    | -   |                                                     |

| 82 | AM335X_GPMC_AD12            | CPU. [GPMC_AD12/LCD_DATA19/MMC1_DAT4/MM C2_DAT0/EQEP2A_IN/PR1_MII0_TXD2/PR1_P RU0_PRU_R30_14/GPIO1_12]  | T12 |                                                     |

| 83 | USB1_DRVVBUS                |                                                                                                         | F15 |                                                     |

| 84 | AM335X_GPMC_AD13            | [GPMC_AD13/LCD_DATA18/MMC1_DAT5/MM<br>C2_DAT1/EQEP2B_IN/PR1_MII0_TXD1/PR1_P<br>RU0_PRU_R30_15/GPIO1_13] | R12 |                                                     |

| 85 | VUSB_VBUS1                  | CPU.USB1_VBUS                                                                                           | T18 |                                                     |

| 86 | AM335X_GPMC_AD14            | CPU.                                                                                                    | V13 |                                                     |

|     | T                     |                                                                              | 1        |  |  |

|-----|-----------------------|------------------------------------------------------------------------------|----------|--|--|

|     |                       | [GPMC_AD14/LCD_DATA17/MMC1_DAT6/MM                                           |          |  |  |

|     |                       | C2_DAT2/EQEP2_INDEX/PR1_MII0_TXD0/PR1                                        |          |  |  |

|     |                       | PRU0_PRU_R31_14/GPIO1_14]                                                    |          |  |  |

| 87  | AM335X_AIN0           |                                                                              | B6       |  |  |

| 88  | AM335X_GPMC_AD15      | = : = :                                                                      | U13      |  |  |

|     |                       | [GPMC_AD15/LCD_DATA16/MMC1_DAT7/MM                                           |          |  |  |

|     |                       | C2_DAT3/EQEP2_STROBE/PR1_ECAP0_ECAP<br>CAPIN_APWM_O/PR1_PRU0_PRU_R31_15/G    |          |  |  |

|     |                       | PIO1 15]                                                                     |          |  |  |

| 89  | AM335X AIN1           |                                                                              | C7       |  |  |

| 90  | AM335X LCD PCLK       |                                                                              | V5       |  |  |

| 30  | AM333X_ECD_I CER      | [LCD PCLK/GPMC A10/PR1 MII0 CRS/PR1 E                                        |          |  |  |

|     |                       | DIO DATA IN4/PR1 EDIO DATA OUT4/PR1 P                                        |          |  |  |

|     |                       | RU1_PRU_R30_10/PR1_PRU1_PRU_R31_10/G                                         |          |  |  |

|     |                       | PIO2_24]                                                                     |          |  |  |

| 91  | AM335X_AIN2           | CPU.AIN2                                                                     | В7       |  |  |

| 92  | DGND                  | DGND                                                                         | -        |  |  |

| 93  | AGND_TSC              | AGND                                                                         | -        |  |  |

| 94  | AM335X_LCD_VSYNC      | CPU.                                                                         | U5       |  |  |

|     |                       | [LCD_VSYNC/GPMC_A8//PR1_EDIO_DATA_IN                                         |          |  |  |

|     |                       | 2/PR1_EDIO_DATA_OUT2/PR1_PRU1_PRU_R3                                         |          |  |  |

| 0.5 | AMAZZEV, AINIZ        | 0_8/PR1_PRU1_PRU_R31_8/GPIO2_22]                                             | . 7      |  |  |

| 95  | AM335X_AIN3           |                                                                              | A7<br>R5 |  |  |

| 96  | AM335X_LCD_HSYNC      |                                                                              | R5       |  |  |

|     |                       | [LCD_HSYNC/GPMC_A9//PR1_EDIO_DATA_IN<br>3/PR1 EDIO DATA OUT3/PR1 PRU1 PRU R3 |          |  |  |

|     |                       | 0 9/PR1 PRU1 PRU R31 9/GPIO2 23]                                             |          |  |  |

| 97  | AM335X AIN4           |                                                                              | C8       |  |  |

| 98  | AM335X_LCD_AC_BIAS_EN |                                                                              | R6       |  |  |

|     |                       | [LCD AC BIAS EN/GPMC A11/PR1 MII1 CRS                                        |          |  |  |

|     |                       | /PR1_EDIO_DATA_IN5/PR1_EDIO_DATA_OUT5                                        |          |  |  |

|     |                       | /PR1_PRU1_PRU_R30_11/PR1_PRU1_PRU_R3                                         |          |  |  |

|     |                       | 1_11/GPIO2_25]                                                               |          |  |  |

| 99  | AM335X_AIN5           |                                                                              | B8       |  |  |

| 100 | AM335X_LCD_DATA0      |                                                                              | R1       |  |  |

|     |                       | [LCD_DATA0/GPMC_A0/PR1_MII_MT0_CLK/EH                                        |          |  |  |

|     |                       | RPWM2A//PR1_PRU1_PRU_R30_0/PR1_PRU1                                          |          |  |  |

| 101 | ACNID TCC             | PRU_R31_0/GPIO2_6]                                                           |          |  |  |

| 101 | AGND_TSC              | AGND                                                                         | -        |  |  |

| 102 | AM335X_LCD_DATA1             | CPU. [LCD_DATA1/GPMC_A1/PR1_MIIO_TXEN/EHR PWM2B//PR1_PRU1_PRU_R30_1/PR1_PRU1_ PRU_R31_1/GPIO2_7]                        | R2  |  |

|-----|------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----|--|

| 103 | AM335X AIN6                  | CPU.AIN6                                                                                                                | A8  |  |

| 104 | AM335X_LCD_DATA2             | CPU. [LCD_DATA2/GPMC_A2/PR1_MII0_TXD3/EHR PWM2_TRIPZONE_INPUT//PR1_PRU1_PRU_R 30_2/PR1_PRU1_PRU_R31_2/GPIO2_8]          | R3  |  |

| 105 | AM335X_AIN7                  |                                                                                                                         | C9  |  |

| 106 | AM335X_LCD_DATA3             | CPU.<br>[LCD_DATA3/GPMC_A3/PR1_MII0_TXD2/EHR<br>PWM2_SYNCI_O//PR1_PRU1_PRU_R30_3/PR1<br>_PRU1_PRU_R31_3/GPIO2_9]        | R4  |  |

| 107 | AGND_TSC                     | AGND                                                                                                                    |     |  |

| 108 | AM335X_LCD_DATA4             | CPU. [LCD_DATA4/GPMC_A4/PR1_MII0_TXD1/EQE P2A_IN//PR1_PRU1_PRU_R30_4/PR1_PRU1_P RU_R31_4/GPIO2_10]                      | T1  |  |

|     | AM335X_ECAP0_IN_PWM0_<br>OUT | CPU. [ECAPO_IN_PWM0_OUT/UART3_TXD/SPI1_CS 1/PR1_ECAP0_ECAP_CAPIN_APWM_O/SPI1_S CLK/MMC0_SDWP/XDMA_EVENT_INTR2/GPI O0_7] | C18 |  |

| 110 | AM335X_LCD_DATA5             | CPU.<br>[LCD_DATA5/GPMC_A5/PR1_MII0_TXD0/EQE<br>P2B_IN//PR1_PRU1_PRU_R30_5/PR1_PRU1_P<br>RU_R31_5/GPIO2_11]             | Т2  |  |

| 111 | AM335X_MMC_D3                | CPU. [MMC0_DAT3/GPMC_A20/UART4_CTSN/TIME R5/UART1_DCDN/PR1_PRU0_PRU_R30_8/PR 1_PRU0_PRU_R31_8/GPIO2_26]                 | F17 |  |

| 112 | DGND                         | DGND                                                                                                                    | -   |  |

| 113 | AM335X_MMC_D2                | CPU.<br>[MMC0_DAT2/GPMC_A21/UART4_RTSN/TIME<br>R6/UART1_DSRN/PR1_PRU0_PRU_R30_9/PR1<br>PRU0_PRU_R31_9/GPIO2_27]         | F18 |  |

| 114 | AM335X_LCD_DATA6             | CPU.<br>[LCD_DATA6/GPMC_A6/PR1_EDIO_DATA_IN6/                                                                           | Т3  |  |

43/79

|     | T                 |                                                  | ı   |  |  |

|-----|-------------------|--------------------------------------------------|-----|--|--|

|     |                   | EQEP2_INDEX/PR1_EDIO_DATA_OUT6/PR1_P             |     |  |  |

|     |                   | RU1_PRU_R30_6/PR1_PRU1_PRU_R31_6/GPI             |     |  |  |

|     |                   | 02_12]                                           |     |  |  |

| 115 | AM335X MMC D1     | CPU.                                             | G15 |  |  |

|     |                   | [MMC0 DAT1/GPMC A22/UART5 CTSN/UART              |     |  |  |

|     |                   | 3_RXD/UART1_DTRN/PR1_PRU0_PRU_R30_1              |     |  |  |

|     |                   | 0/PR1 PRU0 PRU R31 10/GPI02 28]                  |     |  |  |

| 116 | AM335X LCD DATA7  |                                                  | T4  |  |  |

|     |                   | [LCD_DATA7/GPMC_A7/PR1_EDIO_DATA_IN7/            |     |  |  |

|     |                   | EQEP2 STROBE/PR1 EDIO DATA OUT7/PR1              |     |  |  |

|     |                   | PRU1 PRU R30 7/PR1 PRU1 PRU R31 7/G              |     |  |  |